我们很高兴地宣布,DeepSeek-V4 在发布首日即支持推理和强化学习(RL)训练。SGLang 和 Miles 组成了首个开源技术栈,以服务和训练 DeepSeek-V4。这个系统专为其混合稀疏注意力架构、流形约束超连接(mHC)以及 FP4 专家权重而设计。

快速概览

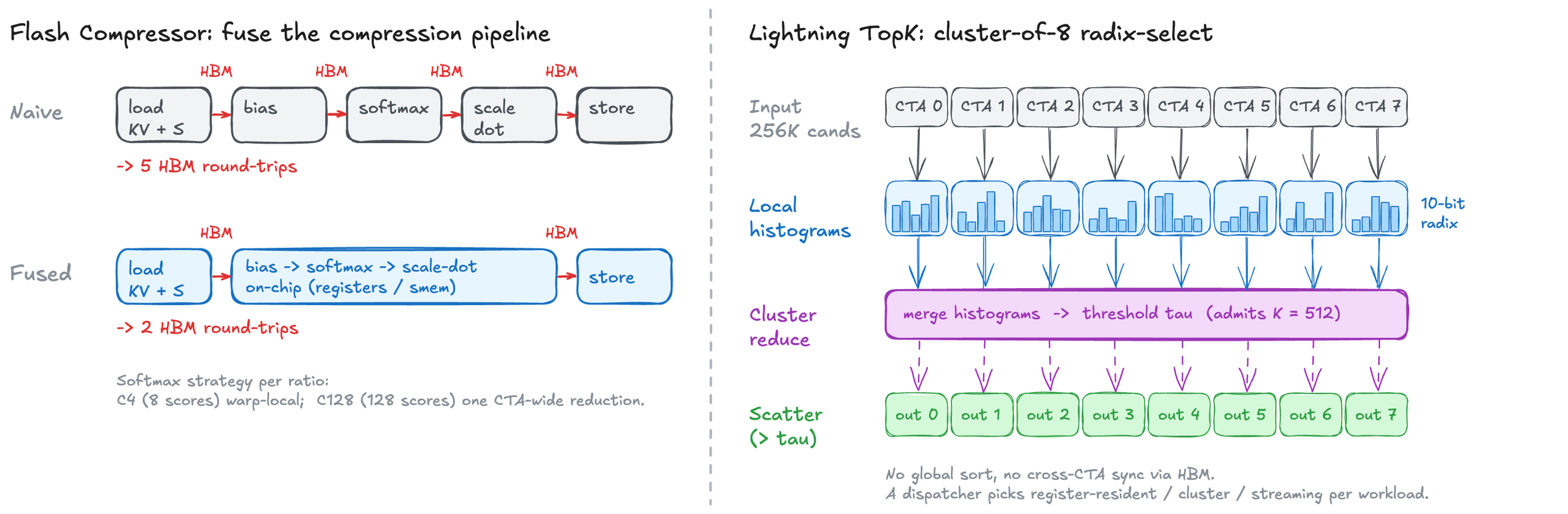

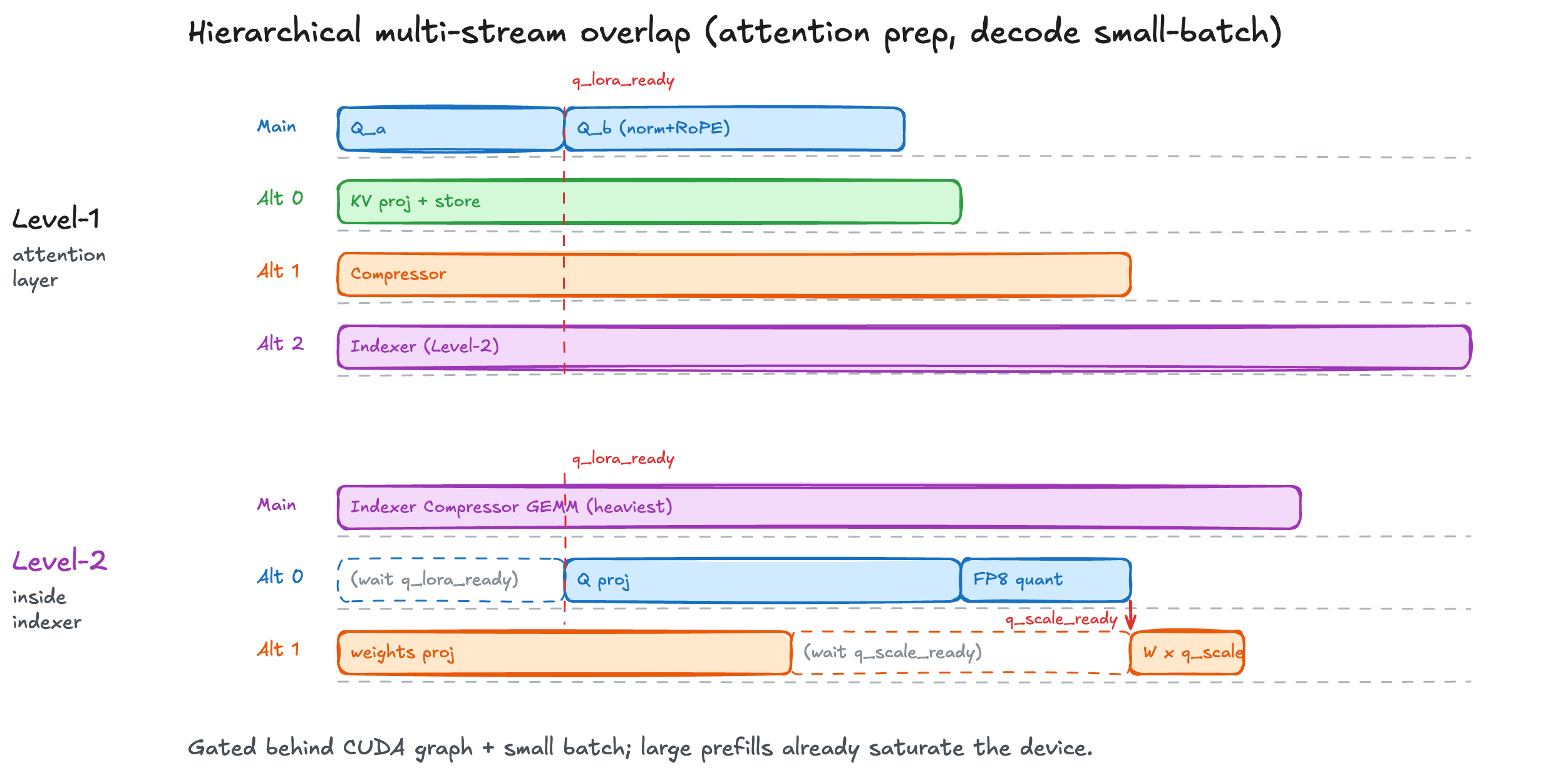

- 推理(缓存与注意力):影子基数前缀缓存、HiSparse CPU 扩展 KV、MTP 推测解码与图内元数据、Flash 压缩器、Lightning TopK、分层多流重叠。

- 推理(内核与部署):快速内核集成(FlashMLA、FlashInfer TRTLLM-Gen MoE、DeepGEMM Mega MoE、TileLang mHC)、DP/TP/CP 注意力、DeepEP 上的 EP MoE、PD 解耦。

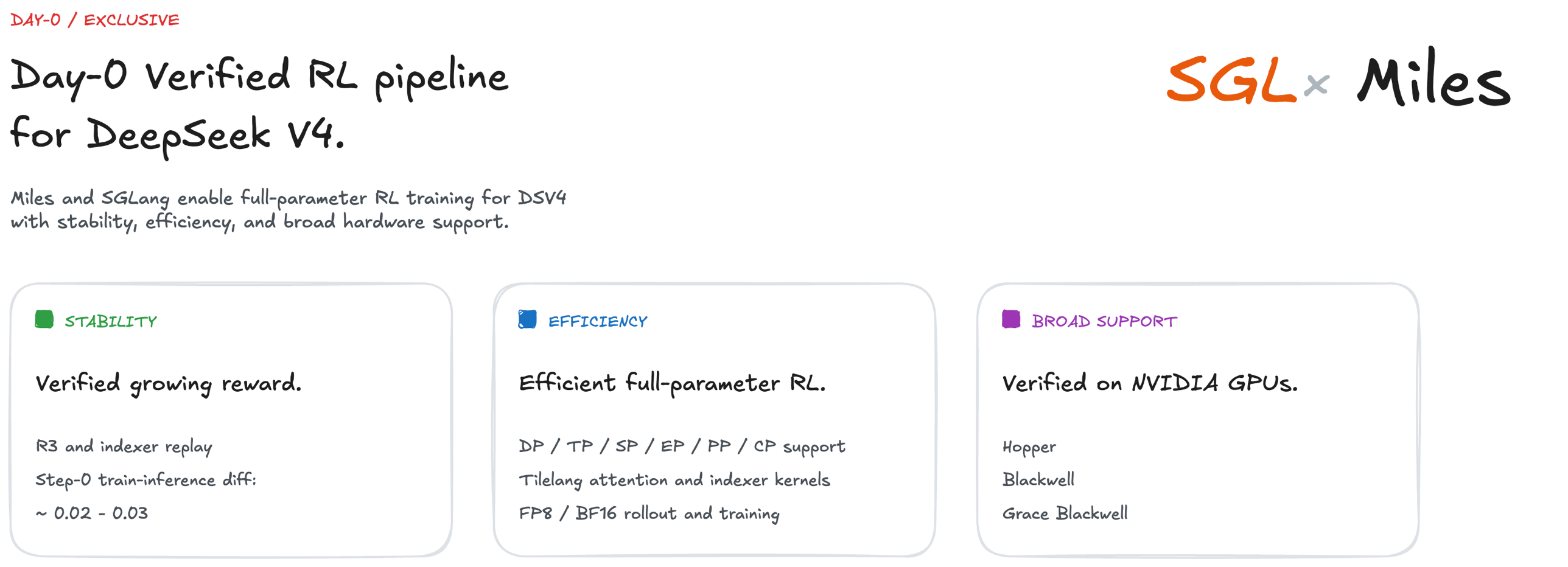

- RL 训练:全并行(DP/TP/SP/EP/PP/CP)、TileLang 注意力、增强稳定性、FP8 训练。

- 硬件支持:Hopper、Blackwell、Grace Blackwell、AMD、NPU。

模型关键特性与新能力

DeepSeek-V4(1.6T Pro,284B Flash)在三个方面扩展了其前身 DeepSeek-V3.2:

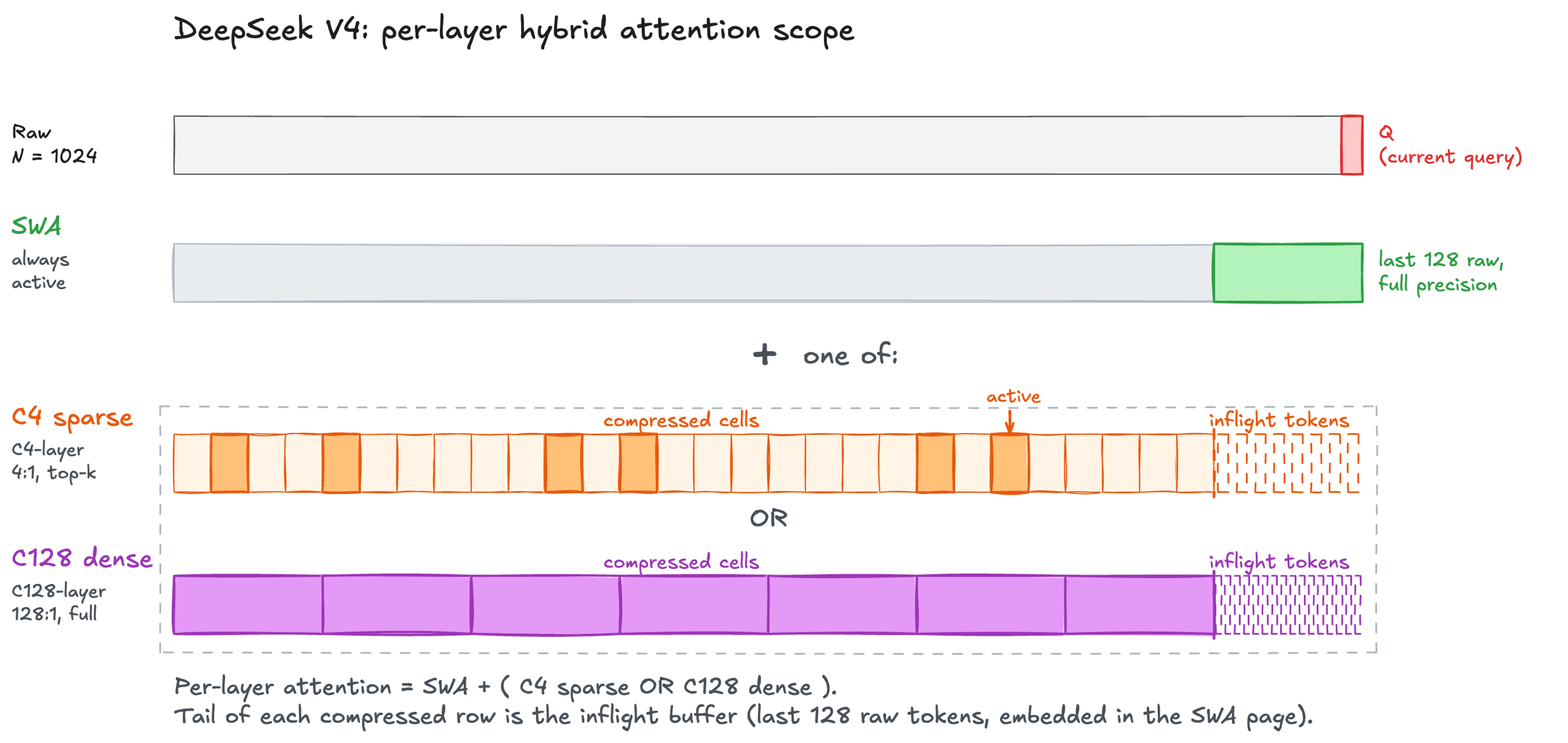

- 混合稀疏注意力:每层混合滑动窗口注意力和两种压缩机制(4:1 top-k 或 128:1 密集),以保持 1M-token 上下文窗口的可控性。

- 流形约束超连接(mHC):标准残差连接的推广,改善梯度流动和表示质量。

- FP4 专家权重:本地 FP4 MoE 专家,便于在最新的 Blackwell 硬件上高效服务。

设计、特性与性能优化

影子基数:混合注意力的本地前缀缓存

DeepSeek-V4 的每层结合了SWA(最近 128 个原始 token 上的滑动窗口注意力)和 C4(4:1 压缩 KV 上的 top-512 稀疏)或 C128(128:1 压缩 KV 上的密集)。为了维护进行中的压缩 KV 槽,每个压缩层有一个状态池,存储进行中的压缩状态。这个复杂机制打破了传统前缀缓存假设:三个异构的 KV 池和两个压缩状态池必须在预填充、解码和推测解码中保持一致。

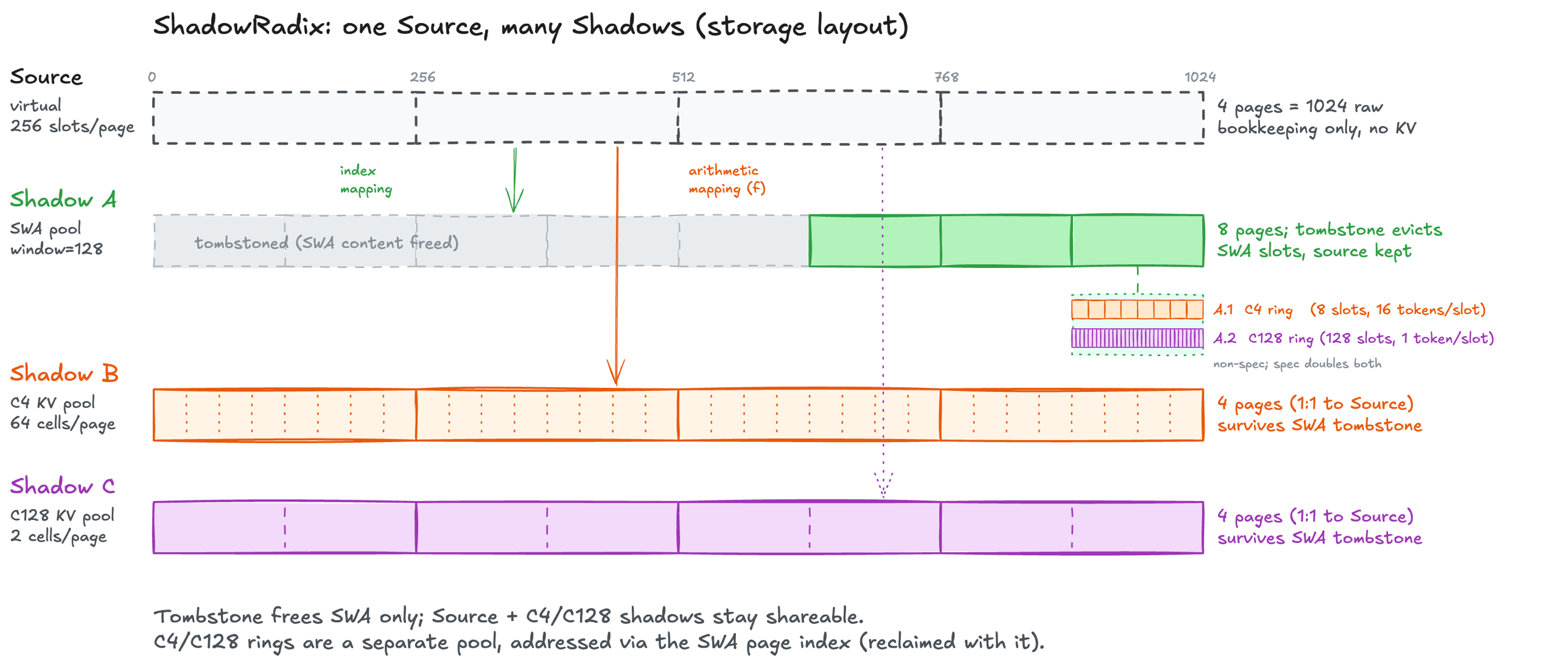

为解决这一一致性问题,我们引入了影子基数,一种用于混合注意力的本地前缀缓存机制。

核心思想是,基数树索引虚拟全 token 槽,这是一种所有层共享的统一坐标系。从每个槽中,我们将影子(每池索引映射)投射到物理池(SWA / C4 / C128)。压缩状态环形缓冲区在其自身池中,但二级算术影子将每个环形槽从 SWA 页面索引映射——在逻辑上嵌套在 SWA 内部,在物理上独立。这使得生命周期的解耦成为可能:墓碑化一旦滑动窗口超过节点,就释放其 SWA 槽,而其 C4/C128 影子保持活跃并可共享。因此,一个 10k-token 请求只保留 128 个 SWA token 及其完整的 C4/C128 压缩 KV——而该压缩 KV 是其他前缀匹配请求所复用的。

推测解码

DeepSeek-V4 配备了单层 MTP 头——一个单独训练的 DSv4 解码层,只运行 SWA 注意力(无压缩器,无索引器),前一步的隐藏状态(h_proj)和下一个 token 嵌入(e_proj)组合为其输入。我们在发布首日支持它;实际系统工作在其下方一层。混合注意力元数据繁重,在调度程序流中提前准备成为推测解码下的启动瓶颈——因此我们将该准备工作融合到 CUDA 图中用于草稿和验证通行。

两项优化带来提速:

- 图内元数据准备。混合注意力的每次通行元数据很重——SWA 页面索引、影子映射池槽、压缩器/索引器计划、每池写入位置——但这都是页面表和长度上的索引算术,适合设备内核。因此,每个捕获的图只需原始批状态作为每重播输入(活动请求、当前长度、新 KV 目的地),复制到固定缓冲区中;捕获的内核在图内重建其余部分,Python 在重播期间从未接触每次通行路径。这将每步启动开销压缩到最低,否则将主导推测解码。

- 重叠调度。CPU 端工作(结果处理、批准备、释放)与 GPU 执行并行运行。

图 3. 混合稀疏注意力结合影子基数和图内推测元数据,使 SGLang 解码吞吐量从 4K 到 900K 基本保持平稳——接近模型完整的 1M 上下文窗口。在 B200(199 -> 180 token/s)和 H200(266 -> 240 token/s)上的下降在 10% 以下。

HiSparse:通过分层内存加速稀疏注意力

最近推出的 HiSparse 是一种技术,它将非活动 KV 缓存卸载到 CPU 内存,从而为稀疏注意力提供更大的批量大小和更高的吞吐量。HiSparse 自然适应于C4 层:每一步索引器 top-k 仅接触一小部分压缩位置,因此大多数 C4 KV 在任何时候都是非活动的,可以存在于 CPU 上。C128 是密集的(每个位置都被触及),SWA 已经很小(128 个 token),因此两者都不能从卸载中受益。通过使用 CPU 内存池仅扩展 C4 KV 缓存池,我们提高了长上下文服务的整体 token 容量和吞吐量,最多可达 3 倍。

左图:GPU 仅保留用于 C4 KV 缓存活动工作集的小型设备缓冲区,而较大的固定 CPU 镜像存储完整上下文 KV 缓存。每一步,HiSparse 协调器从 CPU 中交换未命中页面并使用 LRU 策略驱逐非活动 GPU 页面。新生成的 token 异步备份到 CPU 镜像。右图:在 2xB200 上,[DeepSeek-V4-Flash](https://huggingface.co/deepseek-ai/DeepSeek-V4-Flash) 的峰值吞吐量,200K 输入 / 20K 输出,swa_full_tokens_ratio=0.001。

© 2026 Winzheng.com 赢政天下 | 转载请注明来源并附原文链接